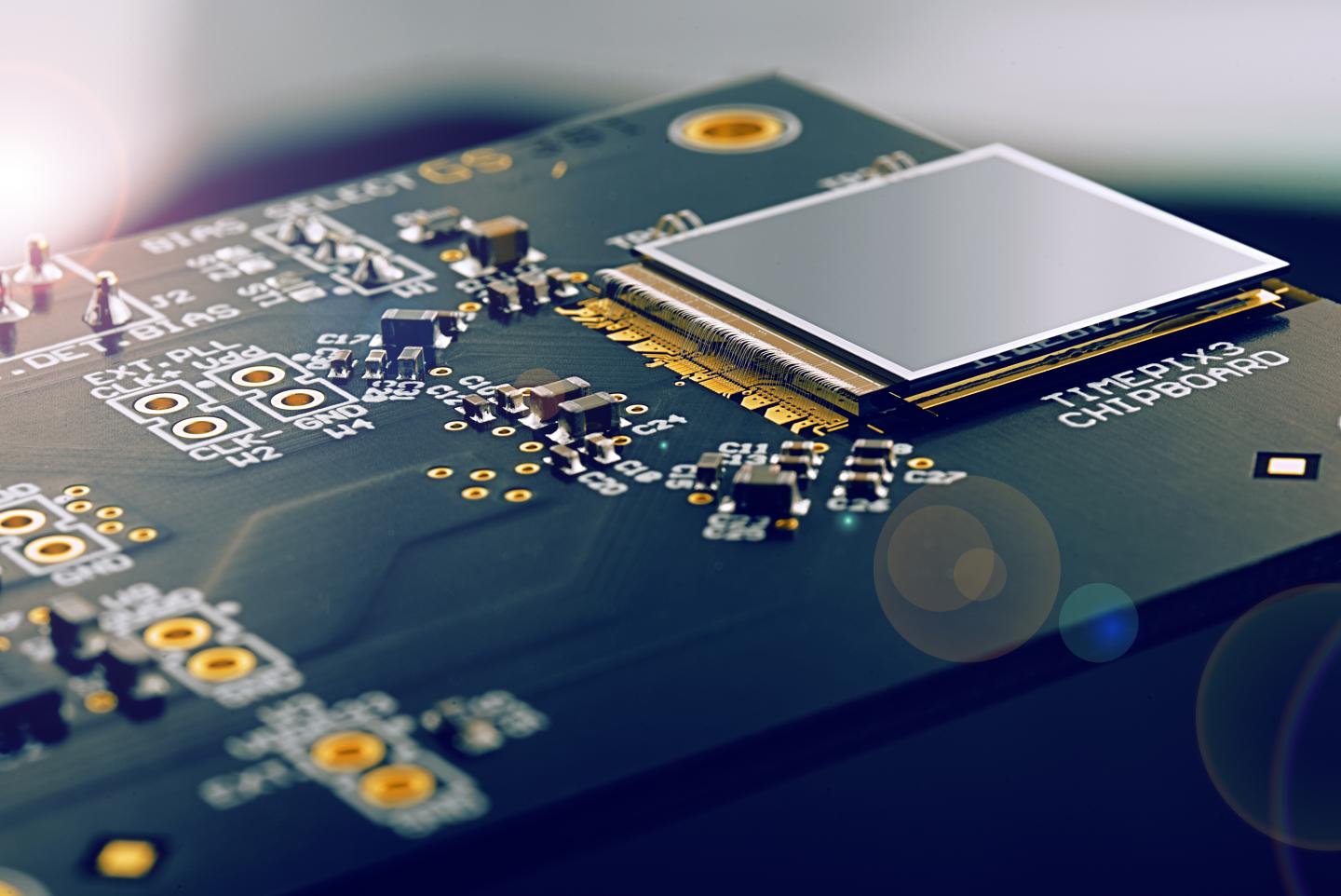

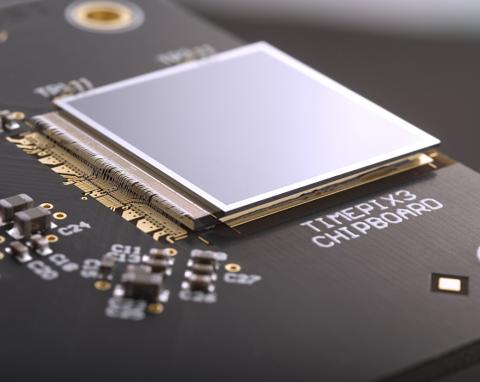

Medipix3 is a CMOS pixel detector readout chip designed to be connected to a segmented semiconductor sensor. Like its predecessor, Medipix2, it acts as a camera taking images based on the number of particles which hit the pixels when the electronic shutter is open. However, Medipix3 goes much further than Medipix2 permitting colour imaging and dead time free operation. A novel charge summing and allocation scheme is implemented at the pixel level permitting proper binning of the energy of incoming photons overcoming the effects of fluorescence and charge diffusion. As there are 2 counters in each 55μm pixel the chip can be programmed such that one counter is being read out while the other is counting. It is also possible to connect the chip to a sensor matrix with a pitch of 110μm. In this way, up to 8 counters are available per pixel.

Advantages & Applications

Features

- Pixel size 55μm x 55μm or 110μm x 110μm

- 256 x 256 or 128 x 128 pixels

- Charge summing and allocation scheme – mitigating charge sharing

- 2 thresholds per 55mm pixel each with 5 bits of local adjustment

- High gain mode (HG, lower linearity, lower noise) or low gain mode (LG)

- Configurable counter depths: 2 x 1-bit, 2 x 4-bit, 2 x 12-bit, 1 x 24-bit

- Continuous or sequential data acquisition and readout

- 3-side buttable (with a single 0.8mm dead edge)

- TSV ready

Applications

- Adaptive optics and other visible or near visible light applications

- Astrophysics

- Background radiation monitoring

- Digital Autoradiography

- Dosimetry

- Education

- Electron microscopy

- Life Sciences

- Neutron imaging

- Various X-ray and gamma-ray imaging applications

- X-ray polarimetry measurements

Specifications

| General | |

|---|---|

| CMOS technology | 0.13 μm |

| Pixel size | 55μm x 55μm |

| Pixel matrix | 256 x 256 |

| Design | CERN |

| Analog front end (pixel cell) | |

|---|---|

| Signal polarity | Positive and negative |

| Leakage current | -10nA to +20nA |

| Time to peak | 120ns |

| Noise |

80 e- (SPM) 175 e- (CSM) |

| Threshold variation (after tuning) | 35 e- rms |

| Minimum operating treshold | 700 e- |

| Digital part (pixel cell + periphery) | |

|---|---|

| Configurable counter depths |

2 x 1-bit 2 x 4-bit 2 x 12-bit 1 x 24-bit |

| 25 DACs (10 9-bit and 15 8-bit) to set voltages in the chip | |

| LVDS drivers and receivers (configuration of the chip in serial mode) | |

| Parallel data port configurable to 1, 2, 4 or 8 LVDS lines | |

| Readout time 8 parallel LVDS lines (200 MHz clock, 12 bit counters) | 491μs |

| Continuous Read/Write | YES |

| Hit rate 28 - 826 Mcounts/mm2/s depending on configuration | |

| Total analog power consumption (nominal conditions) | 440mW |

| Total digital power consumption (@100MHz) | 450mW |